Lithography Workshop 2016

The Hapuna Resort

Kamuela, HI

November 6 – 10, 2016

#### Welcome to the 24th Lithography Workshop!

With the support of its members, the Lithography Workshop has sponsored a unique program which is carefully designed to cover the latest lithography-related advancements to benefit all participants in their field of expertise. The Workshop held its first meeting in Lake Placid, New York in 1981. The 2015 Workshop was the 23rd in a series of meetings that span 34 years promoting the continuing evolution of lithography. The speakers at the Workshop are selected by invitation and represent a broad range of disciplines and covering a wide array of different lithography approaches and requirements. The Workshop is limited to 150 participants.

The Workshop is modeled to be similar to a "Gordon-Research" meeting but with the intent of addressing more immediate issues facing the lithography community within the next few years. The attendees of the Workshop share recent advances and knowledge in lithography with others in the community. The Workshop provides an environment where leading researchers from various disciplines can share their thoughts and ideas. A primary intent is to provide an arena for stimulating debate and the meeting schedule is designed to provide the attendees time for side-meetings and discussions. The Workshop has historically focused on leading-edge semiconductor applications, but has also addressed the challenging lithography needs of flat panel displays, memory devices and 3-dimensional device integration.

This is an opportunity for attendees to meet with world-renown investigators and discuss topics of mutual interest. The Workshop format is intended to provide an atmosphere for in-depth discussions of the invited and poster papers presented. This is accomplished by providing time for extensive questions and answers after each paper, during the poster programs and during group meetings. This year, we will continue with opportunities to present, late-breaking topics of interest. As in the past, there will be no formal proceedings, picture taking, audio or video recording of the Workshop presentations. The technical sessions have been scheduled for mornings and evenings, with time for meetings between attendees and authors during the afternoon. Both invited and late breaking contributing Poster papers will be presented during the evening receptions, prior to the evening oral papers. Please see the Meeting's schedule of events for more information.

The Executive Committee is arranging a program that we believe you will find intellectually stimulating and challenging. Putting together a meeting such as this required the contributions of many people. We are especially thankful to the Technical Program Chairpersons and the Session Chairs who have put together the program. This year, the Technical Program Chair is Dr. Martha Sanchez. Each talk is invited and each speaker is recognized for his/her outstanding work in their field.

We hope that you will avail yourself to all the sessions and functions that the organizers have planned. The Executive Committee welcomes your comments and suggestions to better serve the lithography community.

The Lithography Workshop is very grateful to its sponsors, without whom, we would not be able to continue running the meeting. The LOGOs of our 2016 sponsors are shown on the back cover.

Vivek Singh, Ph.D. President of the Executive Committee

Silver Sponsors of the 2016 Lithography Workshop

### **Bronze Sponsors of the 2016 Lithography Workshop**

### **Bronze Sponsors of the 2016 Lithography Workshop**

## **Bronze Sponsors of the 2016 Lithography Workshop**

#### **The Executive Committee**

**Vivek Singh,** President Intel Corporation vivek.singh@intel.com

**Andrew M. Hawryluk**, Vice-President Ultratech ahawryluk@ultratech.com

Tom Wallow, Treasurer ASML Brion Technologies tom.wallow@asml.com

**Ken Harrison**, Registration Chair HG Engineering Ken.harrison1@verizon.net

John Frankenthaler, Corporate Sponsors F&F Associates FandF@att.net

Larry Zurbrick, Secretary & Publications Keysight Technologies Larry\_Zurbrick@keysight.com **Bruno La Fontaine**

Cymer Bruno La Fontaine@cymer.com

Lars Liebman

IBM Corporation

Iliebman@us.ibm.com

Michael A Guillorn IBM Corporation maguillorn@us.ibm.com

**Tim Crimmins**Intel Corporation

tfcrimmins@gmail.com

Mordechai Rothschild MIT Lincoln Labs rothschild@ll.mit.edu

### **Technical Program Chairs**

# Martha Sanchez IBM Corporation

### **Topical Chairs**

|    | Session                                          | Session Chairs                                                                  |

|----|--------------------------------------------------|---------------------------------------------------------------------------------|

| 1  | Plenary                                          | Martha Sanchez (IBM)                                                            |

| 2  | Design and Device Technology                     | Luigi Capodieci (KnotPrime Inc) Da Yang (QCT) John Sturtevant (Mentor Graphics) |

| 3  | 193i extension and multiple patterning           | Carlos Fonseca (TEL) Richard Schenker (Intel) Donis Flagello (Nikon)            |

| 4  | EUV                                              | P. Naulleau (LBNL)<br>Geert Vandenberghe (imec)<br>Bill Arnold (ASML)           |

| 5  | Maskless technology                              | Deirdre Olynick (MF) Alan Brodie (KLA-Tencor) Marco Wieland (Mapper)            |

| 6  | DSA                                              | Roel Gronheid (imec)<br>Mark Somervell (TEL)                                    |

| 7  | Advanced materials and processes for lithography | Chris Ober (Cornell) Ralph Dammel (EMD Performance Materials)                   |

| 8  | Computational Lithography                        | Bob Socha (ASML)<br>Andres Torres (Mentor Graphics)<br>Kevin Lucas (Synopsys)   |

| 9  | Patterning at 5nm and below                      | Pat Martin (Applied Materials)<br>Martin Brukhardt (IBM)                        |

| 10 | Novel litho                                      | Bruce Smith (RIT) John Petersen (Periodic Structures) Doug Resnick (Canon)      |

| 11 | Non-IC applications                              | S. Wind (Columbia) M. Rothschild (MITLL) D. Pappas (NIST)                       |

| 12 | Metrology                                        | Chris Mack (GS)<br>Alain Diebold (SUNY CNSE)<br>Alex Liddle (NIST)              |

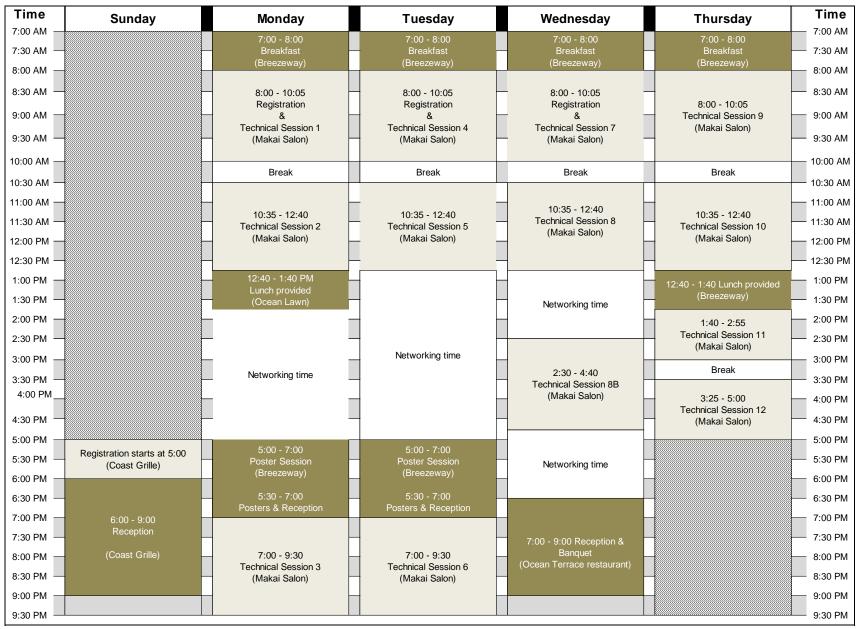

#### **SCHEDULE OF EVENTS**

|           | hedule of Presentations<br>onday, November 7, 2016 |                                                      |                                                                                                                    |      |  |

|-----------|----------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|--|

|           | Time                                               | Presenter                                            | Title                                                                                                              | Page |  |

|           | 8:00 – 8:25 AM                                     | Vivek Singh<br>Martha Sanchez                        | Welcome and Opening Remarks                                                                                        | 1    |  |

| Session 1 | 8:25 – 9:15 AM                                     | Bill Arnold<br>(ASML)<br><i>Keynote Speaker</i>      | EUV Lithography: Current Status and Future Prospects                                                               | 16   |  |

|           | 9:15 – 9:40 AM                                     | Greg Rechtsteiner<br>(Cymer)                         | Effects of DUV light source tunable bandwidth on imaging performance                                               | 17   |  |

|           | 9:40 – 10:05 AM                                    | Eric Hendrickx<br>(imec)                             | EUV insertion possibilities for N7 and N5 technology nodes                                                         | 18   |  |

|           | 10:05 – 10:35 AM                                   | BREAK                                                |                                                                                                                    |      |  |

|           | 10:35 – 11:00 AM                                   | Ankit Vora<br>(IBM Research Almaden)                 | Topcoat-free Strategies for Orientation Control of All-organic High-χ Block Copolymers                             | 20   |  |

|           | 11:00 – 11:25 AM                                   | Michael Thompson<br>(Cornell Univ. / JSR)            | Kinetics of BCP segregation and DSA alignment during millisecond spike annealing                                   | 22   |  |

| Session 2 | 11:25 – 11:50 AM                                   | Nihar Monhanty<br>(TEL Technology Center)            | Patterning when variability rules the roost                                                                        | 23   |  |

| Se        | 11:50 – 12:15 PM                                   | Hiroshi Matsumoto<br>(NuFlare Technology)            | Multi-beam mask writer MBM-1000                                                                                    | 24   |  |

|           | 12:15 – 12:40 PM                                   | Keita Sakai<br>(Canon)                               | A Review of Nanoimprint Wafer and Mask Tool<br>Progress and Status for High Volume<br>Semiconductor Manufacturing  | 25   |  |

|           | 12:40 PM                                           | Lunch provided                                       |                                                                                                                    |      |  |

|           | 5:00 – 7:00 PM                                     | Poster Session                                       |                                                                                                                    | -    |  |

|           | 5:30 – 7:00 PM                                     | Food, Drinks and Posters                             |                                                                                                                    | -    |  |

|           | 7:00 – 7:25 PM                                     | Qi-Huo Wei<br>(Kent State / Liquid Crystal<br>Inst.) | Projection Photo Patterning Molecular Orientations in Liquid Crystals by Using Novel Plasmonic Metamasks           | 27   |  |

|           | 7:25 – 7:50 PM                                     | Hiroshi Fukuda<br>(Hitachi High Technology)          | Electron beam-based metrology and inspection, overcoming the limitation of scaling, variability, and productivity  | 28   |  |

| 3         | 7:50 – 8:15 PM                                     | Mike Rieger<br>(Synopsys)                            | Patterning for advanced integrated devices                                                                         | 29   |  |

| Sior      |                                                    | (-1                                                  |                                                                                                                    |      |  |

| Session 3 | 8:15 – 8:40 PM                                     | Vito Dai<br>(Motivo)                                 | Physical Design Characterization and Optimization with Graph-based Search, Advanced Analytics and Machine Learning | 30   |  |

| Session   | 8:15 – 8:40 PM<br>8:40 – 9:05 PM                   | Vito Dai                                             | with Graph-based Search, Advanced Analytics and                                                                    | 30   |  |

| Session   |                                                    | Vito Dai<br>(Motivo)<br>Tatsuhiko Higashiki          | with Graph-based Search, Advanced Analytics and<br>Machine Learning                                                |      |  |

|           | Schedule of Presentations  Tuesday, November 8, 2016 |                                                          |                                                                                                    |      |  |

|-----------|------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|--|

|           | Time                                                 | Presenter                                                | Title                                                                                              | Page |  |

|           | 8:00 – 8:50 AM                                       | Shinji Okazaki<br>(Gigaphoton)<br><i>Keynote Speaker</i> | Lithography: A key enabler for Moore's law scaling                                                 | 35   |  |

| Session 4 | 8:50 – 9:15 AM                                       | Jean-Pierre Cloarec<br>(Universite de Lyon)              | Collective self-assembly of large sets of nanoparticles on nanopatterned functionalized substrates | 36   |  |

| Se        | 9:15 – 9:40 AM                                       | Ben Bundy<br>(SEMATECH)                                  | HVM metrology for 5 nm                                                                             | 37   |  |

|           | 9:40 – 10:05 AM                                      | Puneet Gupta<br>(UCLA)                                   | Design-Technology_Co-Optimization Applications to EUV and DSA Process Technologies                 | 38   |  |

|           | 10:05 – 10:35 AM                                     | BREAK                                                    |                                                                                                    |      |  |

|           | 10:35 – 11:00 AM                                     | Bernd Geh<br>(Zeiss)                                     | EUV and flexible illumination for 5 nm Lithography and beyond                                      | 40   |  |

| 5         | 11:00 – 11:25 AM                                     | Naoya Hayashi<br>(DNP)                                   | EUV masks                                                                                          | 41   |  |

| Session ! | 11:25 – 11:50 AM                                     | Elmar Platzgummer<br>(IMS Nanofabrication)               | Multi-Beam Mask Writer MBMW-101 for the 7 nm node, and beyond                                      | 42   |  |

| S         | 11:50 – 12:15 PM                                     | Marie Krysak<br>(Intel)                                  | Stochastic and Non-Stochastic CD variations in Next Generation Lithography                         | 43   |  |

|           | 12:15 – 12:40 PM                                     | Deirdre Olynick<br>(LBNL)                                | Elements for EUV Electronic Resist Amplification                                                   | 44   |  |

|           | 12:40 PM                                             | End Session                                              |                                                                                                    |      |  |

|           | 5:00 – 7:00 PM                                       | Poster Session                                           |                                                                                                    | -    |  |

|           | 5:30 – 7:00 PM                                       | Food, Drinks and Posters                                 |                                                                                                    | -    |  |

|           | 7:00 – 7:25 PM                                       | Yuri Granik<br>(Mentor Graphics)                         | Gems and Jams of Inverse Lithography                                                               | 46   |  |

|           | 7:25 – 7:50 PM                                       | F. Joseph Heremans<br>(Univ. Chicago)                    | Localizing Point Defects in Wide Bandgap<br>Semiconductors                                         | 47   |  |

| 9 u       | 7:50 – 8:15 PM                                       | Rene Klavier<br>(Heidenhein)                             | Advantages of maglev stages for metrology and inspection applications                              | 49   |  |

| Session 6 | 8:15 – 8:40 PM                                       | S.V. Sreenivasan<br>(Univ. of Texas)                     | Emerging nanopatterning opportunities in electronics, displays, and healthcare                     | 50   |  |

|           | 8:40 – 9:05 PM                                       | Martin Burkhardt<br>(IBM)                                | Prospect of low-k1 Lithography in EUV                                                              | 51   |  |

|           | 9:05 – 9:30 PM                                       | Robert R. McLeod<br>(Univ. of Colorado<br>Boulder)       | Novel Multiple patterning lithography far beyond the diffraction limit                             | 52   |  |

|           | 9:30 PM                                              | End Session                                              |                                                                                                    |      |  |

|           | Schedule of Presentations |                                                                                     |                                                                                                                                             |      |  |

|-----------|---------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| Wedr      | nesday, November 9, 20    |                                                                                     |                                                                                                                                             | I _  |  |

|           | Time                      | Presenter                                                                           | Title                                                                                                                                       | Page |  |

|           | 8:00 – 8:25 AM            | Nikolaj Gadegaard<br>(Univ. Glasgow)                                                | Cell and Tissue Engineering Based on Micro- and Nanolithography                                                                             | 54   |  |

| 7         | 8:25 – 8:50 AM            | Ricardo Ruiz<br>(HGST, a Western Digital<br>Brand)                                  | Line Roughness in Block Copolymer Thin Films for Lithographic Applications                                                                  | 56   |  |

| Session 7 | 8:50 – 9:15 AM            | John Fourkas<br>(Univ. of Maryland)                                                 | Progress Report on Photoresist Development for<br>Multicolor Lithography                                                                    | 57   |  |

| 0,        | 9:15 – 9:40 AM            | Nicole Lindermann<br>(Nanoscribe GmbH)                                              | 3D Printing for Photonics Applications                                                                                                      | 58   |  |

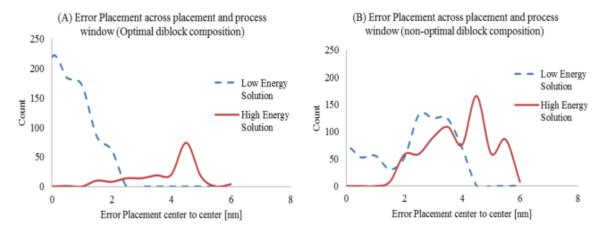

|           | 9:40 - 10:05 AM           | Andres Torres<br>(Mentor Graphics)                                                  | Reducing error placement sensitivity to guiding pattern distortions in cylinder forming DSA by optimizing grapho-epitaxy guiding templates. | 59   |  |

|           | 10:05 – 10:35 AM          | BREAK                                                                               |                                                                                                                                             |      |  |

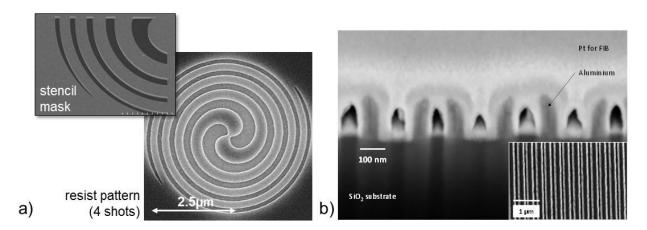

|           | 10:35 – 11:00 AM          | Uwe D. Zeitner<br>(Fraunhofer-Institut für<br>Angewandte Optik und<br>Feinmechanik) | Alternative lithographic technologies for microand nano-optical applications                                                                | 62   |  |

|           | 11:00 – 11:25 AM          | Britt Turkot<br>(Intel)                                                             | To be announced                                                                                                                             | 64   |  |

| Session 8 | 11:25 – 11:50 AM          | Dan Meisburger<br>(Tec-Start Consulting)                                            | The Maskless Lithography Revolution in PCB Production                                                                                       | 65   |  |

| S         | 11:50 – 12:15 PM          | Vassilios Constantoudis<br>(NCSR Demokritos)                                        | Line Edge Roughness is more than just roughness:<br>Recent challenges in LER metrology                                                      | 66   |  |

|           | 12:15 – 12:40 PM          | Hiroki Nakagawa<br>(JSR)                                                            | Novel Spin-on Hard Masks Materials for 5nm Node and Beyond                                                                                  | 68   |  |

|           | 12:40 – 1:10 PM           | Peng Liu<br>(ASML Brion)                                                            | Modeling Challenges in Negative Tone Lithography                                                                                            | 69   |  |

|           | 12:40 PM                  | End Session                                                                         |                                                                                                                                             |      |  |

|         | Schedule of Presentations Wednesday, November 9, 2016 |                                           |                                                                       |      |  |  |  |

|---------|-------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------|------|--|--|--|

|         | Time                                                  | Presenter                                 | Title                                                                 | Page |  |  |  |

|         | 2:30 -2:55 PM                                         | Andrew Khang<br>(UC San Diego)            | Measuring the Design ROI of Patterning Technology Options             | 72   |  |  |  |

| 8B      | 2:55 – 3:25 PM                                        | Christopher Ober<br>(Cornell Univ. / JSR) | EUV metal oxide photoresists: Finding common features between systems | 73   |  |  |  |

| Session | 3:25 – 3:50 PM                                        | Eric Hendrickx<br>(imec)                  | Accurate modeling of EUV mask 3D effects and possible mitigations     | 74   |  |  |  |

|         | 3:50 – 4:15 PM                                        | Ryan Wicker<br>(Univ. of Texas El Paso)   | Printing Multi-Functionality using Additive Manufacturing             | 75   |  |  |  |

|         | 4:15 – 4:40 PM                                        | Soichi Owa<br>(Nikon)                     | Optical lithography potential innovations with near-term feasibility  | 76   |  |  |  |

|         | 4:40 PM                                               | End Session                               |                                                                       |      |  |  |  |

| 6:00 - 6:30 | Reception |  |

|-------------|-----------|--|

| 6:30 - 9:00 | Banquet   |  |

|            | Schedule of Presentations  Thursday, November 10, 2016 |                                                       |                                                                                                                             |      |  |

|------------|--------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|--|

|            | Time                                                   | Presenter                                             | Title                                                                                                                       | Page |  |

|            | 8:00 – 8:50 AM                                         | Richard Schenker<br>(Intel)<br><i>Keynote Speaker</i> | Foundations for 3nm half-pitch patterning                                                                                   | 78   |  |

| 6 u        | 8:50 – 9:15 AM                                         | Patrick Shiavone<br>(Aselta)                          | Why we should escape 1D-centric e-beam lithography flow                                                                     | 79   |  |

| Session    | 9:15 – 9:40 AM                                         | Leo Pang<br>(D2S, Inc.)                               | GPU Accelerated Model-based Mask Data<br>Preparation and Other Computational Applications<br>in Semiconductor Manufacturing | 80   |  |

|            | 9:40 - 10:05 AM                                        | Ravi Kanjolia<br>(EMD Performance<br>Materials)       | Atomic Layer Deposition Materials: Key Enablers for New Processes                                                           | 81   |  |

|            | 10:05 – 10:35 AM                                       | BREAK                                                 |                                                                                                                             |      |  |

|            | 10:35 – 11:00 AM                                       | Grant Willson<br>(Univ. of Texas at Austin)           | Advances in DSA with high $\chi$ silicon containing block copolymers                                                        | 83   |  |

| 10         | 11:00 – 11:25 AM                                       | Thomas Cecil<br>(Synopsys)                            | Model Based Assist Features                                                                                                 | 85   |  |

| Session 1  | 11:25 – 11:50 AM                                       | Hakaru Mizoguchi<br>(Gigaphoton)                      | To be announced                                                                                                             | 86   |  |

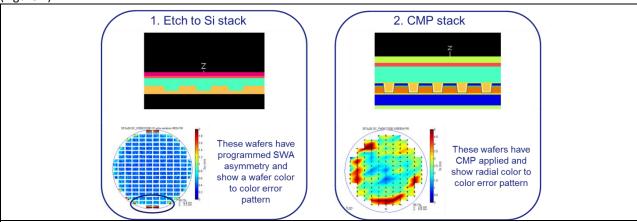

| Š          | 11:50 – 12:15 PM                                       | Eric Bouche<br>(Ultratech)                            | Wafer shape process control in Foundry<br>Lithography                                                                       | 87   |  |

|            | 12:15 – 12:40 PM                                       | Pieter Kruit<br>(Delft / MAPPER)                      | From dose statistics to line edge roughness                                                                                 | 88   |  |

|            | 12:40 – 1:40PM                                         | Lunch provided                                        |                                                                                                                             |      |  |

| 1          | 1:40 – 2:05 PM                                         | Anthony Megrant<br>(Google)                           | Reducing microfabrication-induced loss in superconducting devices                                                           | 90   |  |

| Session 11 | 2:05 – 2:30 PM                                         | Naoya Hayashi<br>(DNP)                                | To be announced                                                                                                             | 91   |  |

| Š          | 2:30 – 2:55 PM                                         | Alex Liddle<br>(NIST)                                 | Defectivity in Self-Assembled Structures                                                                                    | 92   |  |

|            | 2:55 – 3:25 PM                                         | BREAK                                                 |                                                                                                                             |      |  |

|            | 3:25 – 3:50 PM                                         | Shigeki Nojima<br>(Toshiba)                           | Machine learning for DFM applications                                                                                       | 93   |  |

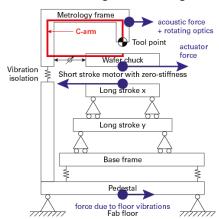

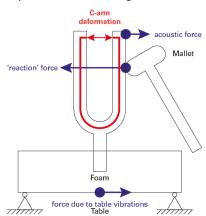

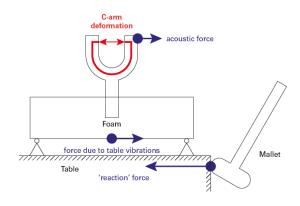

| Session 12 | 3:50 – 4:15 PM                                         | Hamed Sadeghian (TNO)                                 | To be announced                                                                                                             | 94   |  |

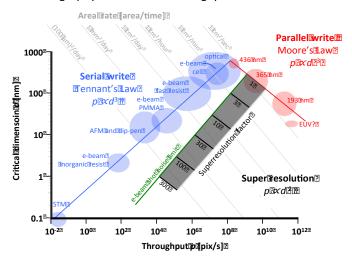

| Ses        | 4:15 – 4:40 PM                                         | Laurent Pain<br>(CEA – Leti)                          | Latest results of MAPPER technology toward its industrialization ramp up                                                    | 95   |  |

|            | 4:40 – 5:00 PM                                         | Martha Sanchez                                        | Closing Remarks and Announcements                                                                                           |      |  |

|            | 5:00 PM                                                | End Session and Conference                            |                                                                                                                             |      |  |

### Poster Papers

### Monday, November 7, 5:00 – 7:00 PM Tuesday, November 8, 5:00 – 7:00 PM

| Presenter                                  | Title                                                                                                                       | Page |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|

| Felix Holzner<br>(SwissLitho AG)           | Pattern transfer of 3D patterns and sub-15 nm half-pitch lines using a variety of hard masks for NanoFrazor lithography     | 97   |

| Felix Holzner<br>(SwissLitho AG)           | 3D NIL stamp fabrication on 200mm wafers with single nanometer resolution using NanoFrazor lithography                      |      |

| Norbert Koster<br>(TNO)                    | Contamination Control for EUV lithography at TNO                                                                            | 98   |

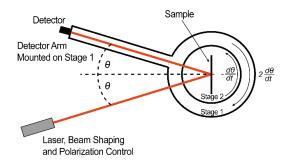

| S.R.J. Brueck<br>(Univ. of New Mexico)     | The CD/Wavelength Limits of Scatterometry                                                                                   | 99   |

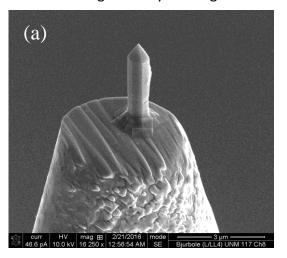

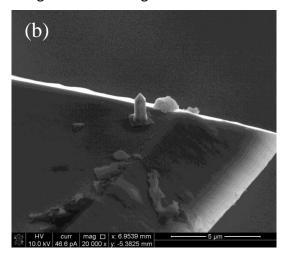

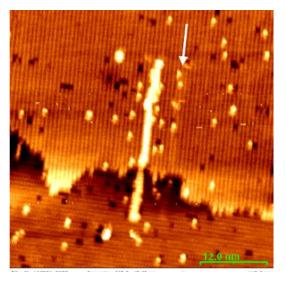

| S.R.J. Brueck<br>(Univ. of New Mexico)     | GaN Tips for Atomic Force Microscopy/Scanning Tunneling Microscopy/Scanning Tunneling Lithography                           | 101  |

| Luigi Capodieci<br>(KnotPrime, Inc.)       | A Novel Data Analytics and Machine Learning Computational Framework for Design For Manufacturability                        | 103  |

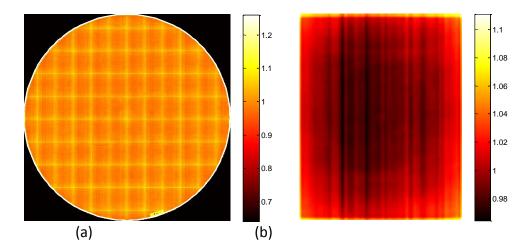

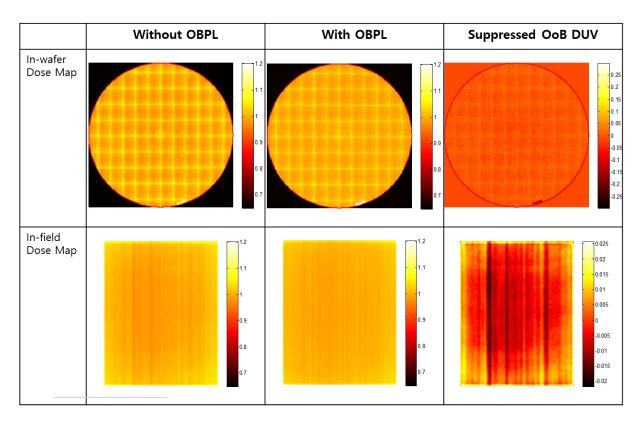

| Jinseok Heo<br>(Samsung)                   | Characteristics of OoB Distributions at the Wafer Level of EUV Lithography Tool                                             | 104  |

| Kazuki Kasahara<br>(Cornell Univ./JSR)     | Nanoparticle photoresist development status for EUV lithography                                                             | 106  |

| Marco Wieland<br>(Mapper)                  | MAPPER: High throughput maskless lithography                                                                                | 107  |

| John S. Petersen<br>(NanoTronix Inc.)      | Exploring the potential of Multiphoton Laser Ablation Lithography (MP-LAL) as a reliable technique for sub-50 nm patterning | 108  |

| Mark Somervell<br>(TEL)                    | Defect Reduction Results for Chemo-Epitaxy DSA Lines                                                                        | 109  |

| Geert Vandenberghe (imec)                  | DSA as patterning option for memory and logic                                                                               | 110  |

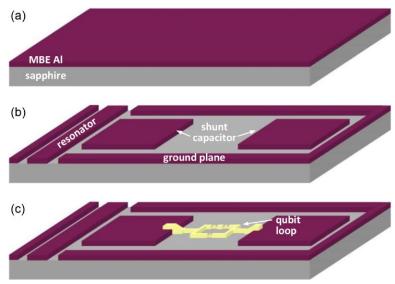

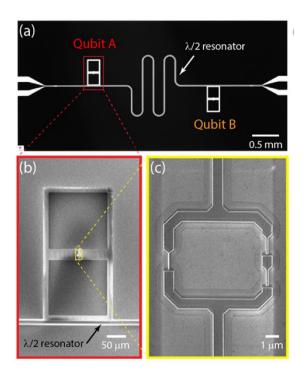

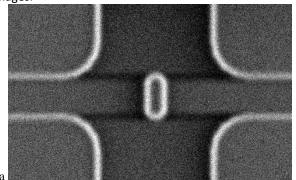

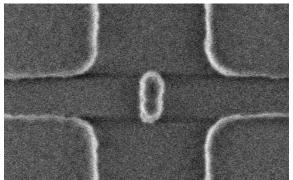

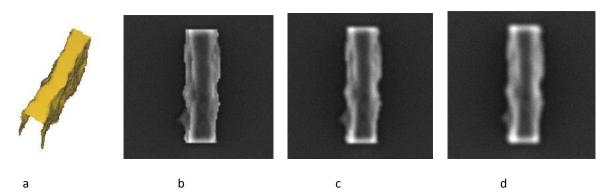

| J. L. Yoder<br>(MIT Lincoln Labs)          | Fabrication of High-Coherence Superconducting Qubits                                                                        | 111  |

| Mary Ann Hockey<br>(Brewer Science, Inc.)  | Back End of the Line (BEOL) Strategy for Directed Self-Assembly                                                             | 113  |

| Tommy Oga<br>(Gigaphoton Inc.)             | The ArF Laser for the next generation cutting-edge ArFi lithography supporting green operations                             | 114  |

| Sergey Babin (aBeam<br>Technologies, Inc.) | Accurate and fast analytical modeling of SEM images                                                                         | 115  |

| Sergey Babin (aBeam<br>Technologies, Inc.) | 1.5 nm fabrication of test patterns for characterization of metrological systems                                            | 116  |

| Dave Pappas<br>(NIST)                      | Fabrication of Josephson junctions                                                                                          | 118  |

| Carlos Fonseca<br>(TEL)                    | Multi-patterning                                                                                                            | 119  |

| Yubing Guo<br>(Kent State University)      | Projection Photopatterning Molecular Orientations with Plasmonic Metamasks                                                  | 120  |

## **Session 1**

# Presentation Schedule for Monday, November 7, 2016

### Session Chair Martha Sanchez

|         | Time             | Presenter         | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 8:00 – 8:25 AM   | Vivek Singh       | Welcome                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | 8:00 - 8:25 AIVI | Martha Sanchez    | Welcome                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |                  | Bill Arnold       | FUNCTION OF THE PROPERTY COMMON AND STATE OF THE PROPERTY OF T |

| n 1     | 8:25 – 9:15 AM   | (ASML)            | EUV Lithography: Current Status and Future Prospects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Session |                  | Keynote Speaker   | Trospects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Se      | 9:15 – 9:40 AM   | Greg Rechtsteiner | EUV Lithography: Current Status and Future                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 3.13 3.40 AIVI   | (Cymer)           | Prospects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 9:40 – 10:05 AM  | Fric Hendrickx    | EUV insertion possibilities for N7 and N5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 3.40 10.03 AW    | Enemenancia       | technology nodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | 10:05 – 10:35 AM | BREAK             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### **EUV Lithography: Current Status and Future Prospects**

William H Arnold

ASML Technology Development Center

2650 West Geronimo Parkway

Chandler, AZ 85284

Email: bill.arnold@asml.com

#### **ABSTRACT**

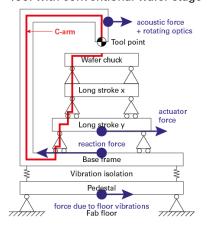

With the advent of 7nm logic and 16nm DRAM, EUV lithography will be inserted for critical levels which otherwise must be defined with inefficient and increasingly uneconomic multi-patterning technology. EUVL has been developed to achieve substantially finer resolution than is available with 193nm immersion lithography in order to support shrinking design rules for CMOS manufacturing.

New manufacturing processes in as fundamental a role as lithography must meet many requirements such as strict variability control, productivity, and cleanliness. As a result, much focus has been brought to optics and mechatronics development, EUV source power improvement, increased tool availability, and the development of an innovative pellicle system [1].

In addition, a roadmap for the future is needed to ensure the further success of nanoelectronics manufacturing. A high numerical aperture scanner is studied for possible introduction for manufacturing in the next decade [2].

Keywords: EUVL, Overlay, Source Power, Pellicle, High Numerical Aperture

#### References:

[1] Alberto Pirati, et al, "EUV Lithography performance for manufacturing: status and outlook", *Proceeding of SPIE, Vol.* 9776, 2016

[2] Jan van Schoot, et al, "EUV high-NA scanner and mask optimization for sub-8nm resolution", *Proceedings of SPIE, Vol. 9776, 2016*

#### Effects of DUV light source tunable bandwidth on imaging performance

Greg Rechtsteiner<sup>a</sup>, Paolo Alagna<sup>b</sup>, Will Conley<sup>a</sup>, Jason Shieh<sup>c</sup>, Simon Hsieh<sup>d</sup>, Tsann-Bim Chiou<sup>c</sup>, Stephen Hsu<sup>e</sup>

a Cymer LLC, San Diego, CA USA b Cymer LLC, Leuven, Belgium c ASML TDC, Hsinchu, Taiwan d Cymer LLC, Hsinchu, Taiwan e ASML Brion, San Jose, CA USA

The performance requirements of advanced semiconductor technology nodes necessitate the use of complex processing methods that push patterning beyond the physical limits of DUV immersion lithography (ArFi). Specifically, aggressive process window (PW) and yield specifications put tight requirements on scanner imaging performance. As demonstrated by recent studies [1-4], a significant improvement to multiple patterning solutions can be achieved by leveraging light source capabilities.

This study will focus on the increase in image contrast that 200 fm light source E95 bandwidth enables on Self-Aligned Double Patterning (SADP) features. The impact of 200 fm E95 bandwidth on the CD and Edge Placement Error (EPE) performance of core (grating) and block features will be assessed using an imec 7 nm process node test vehicle.

The on wafer experimental results will be compared with simulations on the increase in image contrast that Source Mask Optimization (SMO) and OPC models deliver when using 200 fm light source E95 bandwidth. Using multiple patterning layouts that are aligned with projected 7 and 5 nm process node ground rules, improvements in Exposure Latitude (EL), Critical Dimension (CD) and Mask Error Enhancement Factor (MEEF) performance will be assessed when SMO and OPC are optimized for 200 fm light source bandwidth and compared with the standard 300 fm bandwidth.

- [1] P. Alagna et al., "Optimum ArFi laser bandwidth for 10nm node logic imaging performance", Proc. SPIE 9426, Optical Microlithography XXVIII, 942609 (2015).

- [2] P. Alagna et al., "Lower bandwidth and its impact on the patterning performance", Proc. SPIE 9780, Optical Microlithography XXIX, 978008 (2016).

- [3] W. Conley et al., "Impact of bandwidth on contrast sensitive structures for low k1 lithography", Proc. SPIE 9426, Optical Microlithography XXVIII, 942607 (2015).

- [4] W. Conley et al., "Impact of bandwidth variation on OPC model accuracy", Proc. SPIE 9780, Optical Microlithography XXIX, 9780K (2016).

#### **EUV insertion possibilities for N7 and N5 technology nodes**

Christopher Wilson<sup>a</sup>, Stephane LaRiviere<sup>a</sup>, Bogumila Kutrzeba Kotowska<sup>a</sup>, Danilo De Simone<sup>a</sup>, Joost Bekaert<sup>a</sup>, Jeroen Van de Kerkhove<sup>a</sup>, Peter De Bisschop<sup>a</sup>, Ming Mao<sup>a</sup>, Geert Vandenberghe<sup>a</sup>, Kurt Ronse<sup>a</sup>, Ryoung-han Kim<sup>a</sup>, Eric Hendrickx<sup>a</sup>

EUV lithography has seen rapid progress over the last 2 years. ASML NXE:3300 production tools have been installed at the main chipmakers, and are being tested for pilot production. Most importantly, the rapid improvement in EUV source power has restored credibility to the source roadmap and is a key enabler of the technology. Overall the technology is at the doorstep of production. In this presentation we will review the status of the EUV resists, masks, and scanner, and how these improvements come together in foundry-equivalent N7 and N5 BEOL process modules that are developed at imec to demonstrate the readiness of EUV technology.

We have used the ASML NXE 3300 to fabricate foundry-equivalent N7 product like wafers with both trench and via patterns. Here, compared to 193i, EUV offers the possibility of a single print for advanced nodes. For comparison, we have also developed and tested 193i lithography based flows using multiple litho etch (LE) and doubling pattering (SADP+Keep) to reach sub resolution pitch. The EUV single print flow showed better CDU but slightly worse LWR when compared to the 193i lithography based flows. In either case CDU and LWR can lead to open or bridging. Overlay, lithoetch bias uniformity and line end pull back were key issues to solve in developing these 193i lithography based flows. Greater corner rounding was observed in both the litho etch and litho-etch and double pattering flows when compared to the EUV single print flow. This resulted in clearly better patterning fidelity in the EUV single print flow compared to the 193i lithography based solutions.

Towards the foundry-equivalent N5 technology nodes, a patterning exercise is ongoing for a new imec BEOL process module. Here the metal patterning is done by combining an SAQP grating, fabricated by 193i, and a block layer printed using EUV lithography. We review 2D imaging results from the N5 like block layer for metal patterning. This includes using a metal containing resist, and includes etch transfer with a variety of chemistries. We show the different patterning options, and present experimental results obtained from imec's BEOL N5 EUV platform, with focus on litho performance and process integration.

## Session 2

# Presentation Schedule for Monday, November 7, 2016

### Session Chairs Carlos Fonseca Patrick Naulleau

|           | Time             | Presenter                                    | Title                                                                                                             |

|-----------|------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

|           | 10:35 – 11:00 AM | Ankit Vora<br>(IBM Research<br>Almaden)      | Topcoat-free Strategies for Orientation Control of<br>All-organic High-χ Block Copolymers                         |

|           | 11:00 – 11:25 AM | Michael Thompson<br>(Cornell Univ. / JSR)    | Kinetics of BCP segregation and DSA alignment during millisecond spike annealing                                  |

| Session 2 | 11:25 – 11:50 AM | Nihar Monhanty<br>(TEL Technology<br>Center) | Patterning when variability rules the roost                                                                       |

|           | 11:50 – 12:15 PM | Hiroshi Matsumoto<br>(NuFlare<br>Technology) | Multi-beam mask writer MBM-1000                                                                                   |

|           | 12:15 – 12:40 PM | Keita Sakai<br>(Canon)                       | A Review of Nanoimprint Wafer and Mask Tool<br>Progress and Status for High Volume<br>Semiconductor Manufacturing |

|           | 12:40 AM         | End Session                                  |                                                                                                                   |

# Topcoat-free Strategies for Orientation Control of All-organic High-χ Block Copolymers

Ankit Vora<sup>1\*</sup>, Joy Y. Cheng<sup>1</sup>, Melia Tjio<sup>1</sup>, Noel Arellano<sup>1</sup>, Kristin Schmidt<sup>1</sup>, Anindarupa Chunder<sup>1</sup>, Teddie Magbitang<sup>1</sup>, Elizabeth Lofano<sup>1</sup>, Hsinyu Tsai<sup>2</sup>, Hiroyuki Miyazoe<sup>2</sup>, and Daniel P. Sanders<sup>1</sup>

<sup>1</sup> IBM Research - Almaden, 650 Harry Road, San Jose, CA 95120 <sup>2</sup> IBM Watson Research Center, 1101 Kitchawan Road, Yorktown Heights, NY, 10598

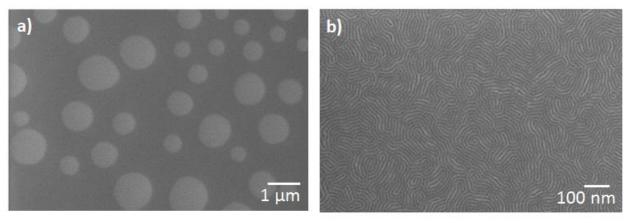

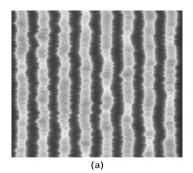

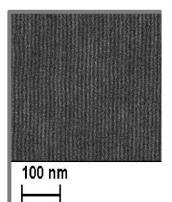

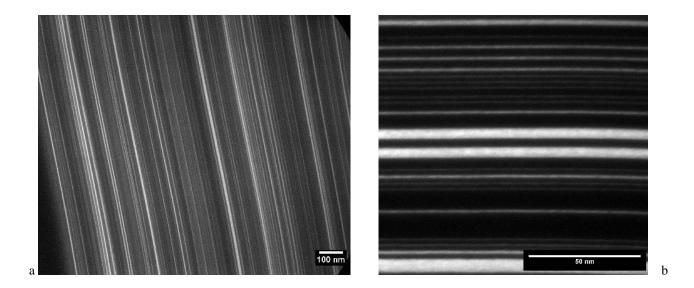

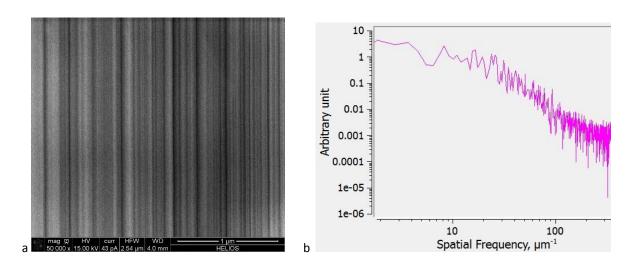

Directed self-assembly (DSA) of block copolymers (BCP) is a promising candidate for extending the patterning capability of conventional lithography. While PS-b-PMMA is the most widely used block copolymer for DSA, the minimum half-pitch of this BCP is limited to ~10nm because of the low interaction parameter ( $\chi$ ) between PS and PMMA blocks. Higher- $\chi$  BCPs (e.g. PS-b-PEO, PS-b-PZVP, PS-b-PTMSS, etc.) capable of smaller natural period, the L0, are expected to be necessary for patterning for sub-10nm IC (integrated circuit) devices. But due to the increased mismatch in the surface energies of the two blocks of high- $\chi$  BCP, only the lower surface energy block is present at the polymer-air interface, rendering the thin-film undesirable for lithographic applications. Previously, we had discussed a formulation-based approach in which a surface active polymer (SAP) was added as an additive to enable perpendicular orientation control of polycarbonate-containing high- $\chi$  BCPs (Figure 1) using a coat and a short thermal annealing step on neutral underlayer modified substrates (Gen. 1 BCP).

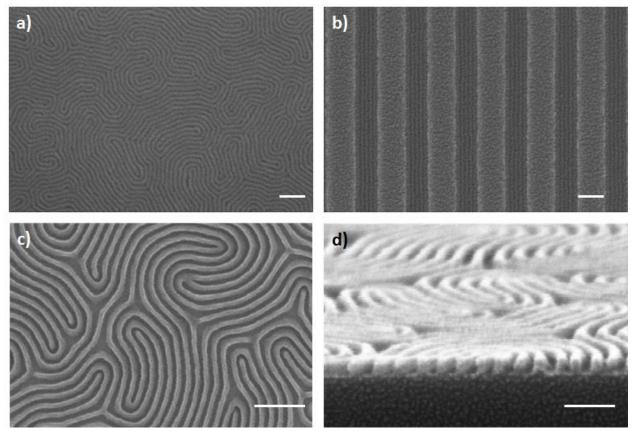

To further improve the robustness of the BCP material and make it more integration-friendly for DSA processing, an additive free high- $\chi$  BCP platform (Gen. 2 BCP, Figure 2) that forms vertically oriented features upon thermal annealing on a wide range on underlayer compositions was developed. In this talk, the development and performance of Gen 2. BCP platform will be discussed. Specifically, the thin-film characterization by AFM and GISAXS to confirm perpendicular orientation, and the effect of thermal annealing conditions and underlayer composition on self-assembly behavior of the lamellae forming BCPs will be detailed. Next, the DSA, etch, and pattern transfer of the Gen. 2 BCP will be highlighted. Finally, the advantages and the limitations of Gen. 1 and Gen. 2 high-  $\chi$  BCPs will be compared with respect to sub-20 nm pitch patterning.

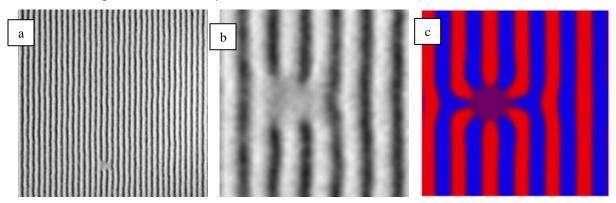

Figure 1. Thin film self-assembly of 19.5 nm pitch polystyrene-*b*-polycarbonate BCP (Gen. 1 BCP) on neutral underlayer modified substrate, a) without SAP additive and b) with 3 wt. % SAP additive. BCP films were annealed at 170 °C for 5 minutes.

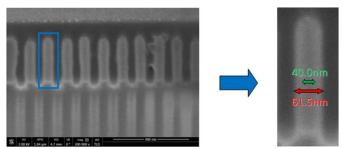

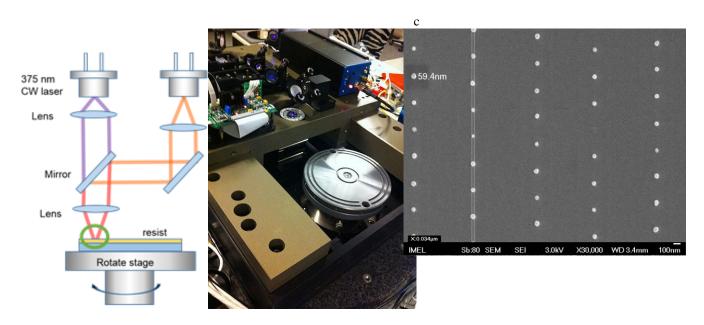

Figure 2. Vertically oriented features for 18.3 nm pitch Gen. 2 BCP upon thermal annealing at 170 °C for 5 minutes. a) fingerprint patterns on neutral underlayer modified substrate, b) 5X graphoepitaxy DSA on prepattern prepared by 193 nm interference lithography, c) Top-down and d) Cross-section SEM images of  $^9$  nm HP BCP fingerprint patterns after removing one of the blocks of the BCP. Scale bar = 100  $\mu$ m.

#### Kinetics of BCP segregation and DSA alignment during millisecond spike annealing

Michael O. Thompson, Alan G. Jacobs, Jing Jiang, Christopher K. Ober, Materials Science and Engineering, Cornell University, Bard Hall, Ithaca, NY 14853

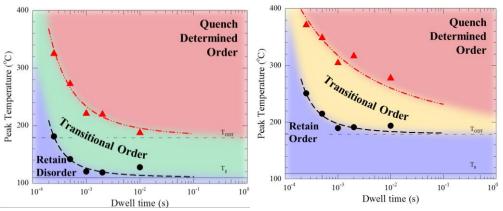

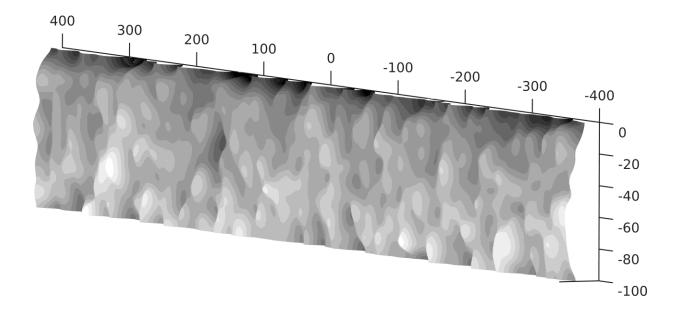

Directed Self Assembly (DSA) of block copolymers (BCP) remains a key potential technology for patterning at sub-7 nm nodes. Achieving requisite alignment precision and reliability, while addressing line edge roughness and etch selectivity, requires understanding of fundamental segregation processes and exploration of alternate processing. In this work, we used millisecond thermal annealing, induced by laser spike annealing (LSA), to map the kinetics of BCP phase segregation and understand the role of this annealing on the eventual development of alignment order during graphoepitaxially directed DSA.

LSA annealing near or above the ODT (order-disorder transformation temperature) can dramatically improve the fidelity of DSA alignment. The early stage segregation behavior, which impacts this final structure, were explored using a later-gradient LSA method with micro-beam grazing incidence small angle X-ray scattering. Ordering and disordering kinetics of cylinder forming PS-b-PMMA were determined for annealing temperatures up to 550 °C and dwells ranging from 250 25 to 10 ms. Both ordering and disordering kinetics were independently monitored. From initially microphase segregated films, disordering began near the equilibrium ODT temperature for dwell times above 10 ms. For shorter times, this disorder is kinetically delayed increasing by over 70°C for 250 2s with asymptotic behavior for times below 50 2s. The onset of ordering from initially disordered films was similarly kinetically limited. For anneals to temperatures well above the ODT, films become fully disordered and the final segregation behavior is determined solely by the thermal quench rate through the ODT and to the glass transition temperature. This results in a history independent final state that forms the initial configuration for further thermal annealing. This kinetic behavior can be represented on an effective Tg and ODT temperature phase map as a function of the heating timescale (figure 1). Thermal processing of the BCP to retain or intentionally modify the initial state can thus be independently managed with accelerating kinetics for other chemical or structural alignment processes at the extreme temperatures.

Graphoepitaxial DSA is enabled by dramatic increases in polymer chain mobility at these temperatures. Optimal DSA alignment was observed with LSA anneals in the 5-20 ms range, still well before polymer decomposition can occur. Effects of laser power, dwell time, underlayer and graphoepitaxy were examined with long range order and alignment achieved with 20 ms laser annealing.

Figure 1: Kinetic phase map for segregation behavior as a function of annealing dwell for initially disordered films (left) and initially ordered films (right).

#### Patterning when variability rules the roost

Nihar Mohanty, Jeffrey Smith, Anton deVilliers, Hidetami Yaegashi, Richard Farrell, Ben Rathsack, Carlos Fonseca, Akiteru Ko, Steven Scheer, Peter Biolsi

TEL Technology Center America, LLC. NanoFab South, Ste. 214, Albany, NY 12202 corresponding email: nihar.mohanty@us.tel.com

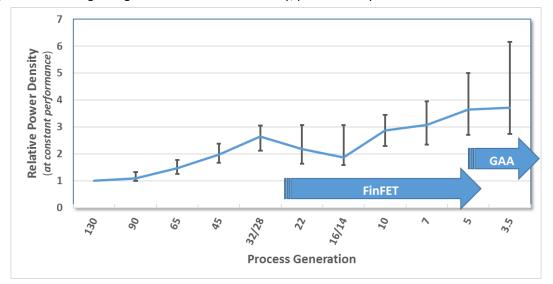

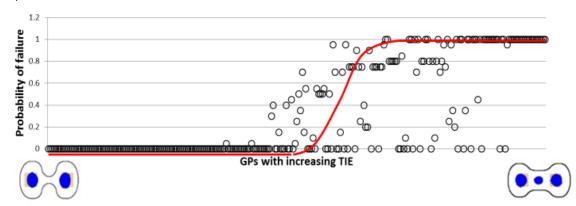

Ever since the Moore's law was first coined, the semiconductor industry has diligently followed the path where making devices smaller resulted in lower price per transistor, higher performance gain and more profits. While in the beginning lithographic advances played a major role in enabling the regular cadence of areal shrinkage, in the recent past, materials and smart integration have been instrumental in assisting lithography for continued scaling. As the industry marches on to the 5nm node and beyond, scaling has slowed down, with all major IDMs & foundries predicting a 3-4 year cadence for scaling. A major reason for this slowdown is not the technical challenge of making features smaller, but effective control of the variation that creeps into the fabrication process. That variability manifests itself as edge placement error (EPE) which has a direct impact on wafer yield (Figure – 1). Resolving EPE concerns necessitates an integrated approach between unit process, materials development, process integration and design.

$$EPE_{random} = \sqrt{\left(\frac{\sigma_{CD1}}{2}\right)^2 + \left(\frac{\sigma_{CD2}}{2}\right)^2 + \left(\frac{\sigma_{CD3}}{2}\right)^2 + \left(\frac{\sigma_{CD4}}{2}\right)^2 + \left(\sigma_{OL1}\right)^2 + \left(\sigma_{OL2}\right)^2 + \left(\sigma_{OL3}\right)^2 + \left(\sigma_{OL4}\right)^2}$$

$$CD \text{ variability includes}$$

$$CDU, LCDU \& LER/LWR$$

$$Overlay \text{ is dominant for } EPE$$

Figure 1: Both CD variability and overlay form major contributors to the EPE. EPE is one of the most critical variability issues faced by the semiconductor industry today.

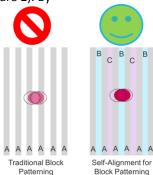

In this paper we will provide a brief overview of our current and upcoming EPE and overlay improvement techniques with special emphasis on self-alignment & self-healing based approaches. The key enabler for most self-alignment based approaches is the ability to trade-off the un-manageable overlay requirement with that of a more manageable etch selectivity requirement (Figure 2). By

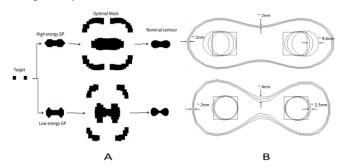

Figure 2: Comparison of traditional vs. self-alignment based patterning showing how by a multi-color material integration, the overlay variation becomes in-consequential thereby reducing the over all EPE. The black lines labelled A are spacer-formed-lines with space being the trench and red ellipse is the block pattern. As evident from the figure, any overlay variation could cause the adjacent trench to get un-intentionally blocked. To enable self-alignment we fill every other trench with a different sacrificial material labeleld B and C. By having high selectivity between A, B and C, self-alignment of blocks can be achieved. This precludes any variation from block pattern overlay.

appropriate choice of different mask and stack materials this etch selectivity challenge can be made trivial. We will present several case studies for both logic & memory, which would cover some of the most critical layer patterning, where we will demonstrate how the implementation of self-alignment & self-healing alleviates key variability concerns. Further, we will also present on the design advantage that the new approaches provide based on common standard cell designs and their potential for simplifying or shortening the design technology co-optimization (DTCO) process during development lifecycle of a technology node. We will conclude the talk with our view on the future direction for industry on patterning & design as a major tool maker.

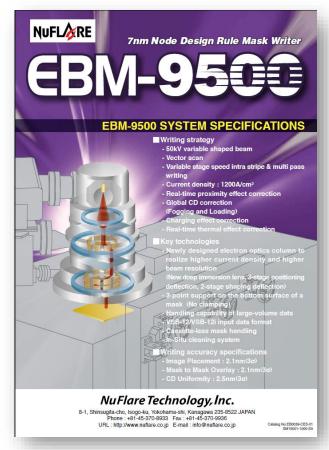

#### Multi-beam mask writer MBM-1000

Hiroshi Matsumoto, Hiroshi Yamashita, Kenji Ohtoshi, Hirokazu Yamada NuFlare Technology, Inc

Progress of shrinkage of semiconductor devices has slowed down, but strong motivation for further shrinkage persists. ArF immersion lithography has been extended by introducing multiple patterning and aggressive OPC. Continuous efforts on EUV lithography accomplished increase of light source enabling pilot fabrication. Evolution of lithography and shrinkage of device pause challenges for mask writers in terms of increase of shot count, number of photomasks and exposure dose as well as more and stringent writing accuracy.

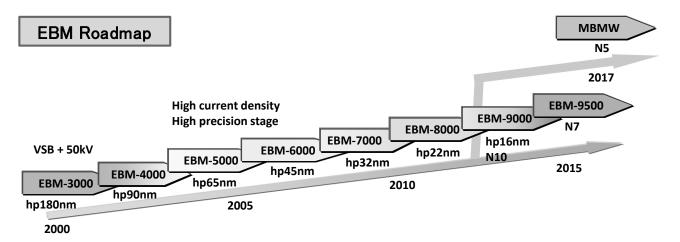

Single variable shaped beam (S-VSB) writer has been used for advanced photomasks in recent decades, but big leap in shot count likely demanded by aggressive OPC or EUV lithography will trigger switch to multi-beam writers. Aiming application to N5, we will launch MBM-1000, our 1<sup>st</sup> product of multi-beam mask writer based on system with blanking aperture array (BAA).

In this paper, we will introduce features of our MBM-1000 with comparison to S-VSB writers, to discuss suitable application field in lithography for MBM-1000 and S-VSB writers. We will also report results of patterning test with MBM-1000 alpha tool.

Figure: History of mask writers in NuFlare Technology Inc.

# A Review of Nanoimprint Wafer and Mask Tool Progress and Status for High Volume Semiconductor Manufacturing

#### Keita Sakai

Canon Inc., 20-2, Kiyohara-Kogyodanchi, Utsunomiya-shi, Tochigi 321-3292 Japan

Imprint lithography has been shown to be an effective technique for replication of nano-scale features. Jet and Flash Imprint Lithography\* (J-FIL\*) involves the field-by-field deposition and exposure of a low viscosity resist deposited by jetting technology onto the substrate. The patterned mask is lowered into the fluid which then quickly flows into the relief patterns in the mask by capillary action. Following this filling step, the resist is crosslinked under UV radiation, and then the mask is removed, leaving a patterned resist on the substrate.